|

En este trabajo se presenta el diseño e implementación de un inversor trifásico tolerante a fallas. Este fue diseñado de modo tal que detecte tres tipos diferentes de fallas y, frente a la presencia de alguna de ellas, se reconfigure de modo de permitir que el sistema del cual forma parte siga funcionando sin necesidad de interrumpir el proceso. Este inversor cuenta con una cuarta rama que entra en funcionamiento mediante un esquema de relés cuando se detecta una falla en alguna de las tres ramas que componen el inversor base. Se presentan resultados experimentales que muestran el correcto funcionamiento del esquema propuesto.

Palabras clave: Inversor trifásico. Tolerancia a fallas

Introducción

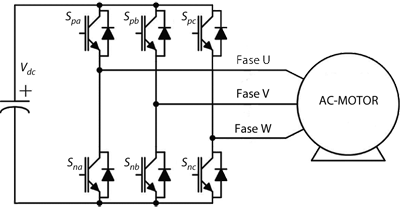

Figura 1. Inversor trifásico con su carga Para determinadas aplicaciones de potencia es necesario, en alguna de sus etapas, la provisión a una determinada carga trifásica de tensiones senoidales de amplitud y frecuencia variables. Estas tensiones son provistas por convertidores de potencia conocidos como inversores trifásicos. Figura 1. Inversor trifásico con su carga Para determinadas aplicaciones de potencia es necesario, en alguna de sus etapas, la provisión a una determinada carga trifásica de tensiones senoidales de amplitud y frecuencia variables. Estas tensiones son provistas por convertidores de potencia conocidos como inversores trifásicos.

En algunas implementaciones, especialmente en aquellas que contienen motores de inducción trifásicos controlados, se pueden requerir garantías de operación continua. En esas condiciones es deseable contar con inversores trifásicos que sean tolerantes a fallas. La posibilidad de tener un convertidor de este tipo permite evitar la redundancia de equipamiento que puede resultar costosa y voluminosa.

Existen varios aspectos que contribuyen a una mayor eficiencia de los inversores, desde el punto de vista constructivo podemos hablar de buenos diseños de PCB, correctas elecciones de los componentes, depuraciones exhaustivas de los algoritmos de control, entre otros. Sin embargo siempre existe la posibilidad de encontrarse, en algún momento de la vida útil del equipo, con alguna situación de falla.

Desde el punto de vista funcional, existen configuraciones circuitales que mejoran la fiabilidad y permiten un funcionamiento continuo. Una forma de aumentar la fiabilidad en los inversores trifásicos es mediante un diseño que contemple el agregado de redundancia en el circuito de modo tal que el convertidor pueda ser tolerante a un cierto número de fallas que puedan presentarse en él.

Existen distintas topologías tolerantes a fallas, referidas al inversor como Welchko et al. (2003), Fu y Lipo (1993) y referidas al motor, cuando este es la carga, como por ejemplo Liu et al. (1993), Yznaga Blanco et al. (2008), Nacusse et al. (2012).

En este trabajo se elige una de las topologías presentadas en Welchko et al. (2003) en la cual se propone la redundancia como el método principal para asegurar la fiabilidad de los inversores trifásicos. Basándose en este concepto se explicarán los aspectos básicos a tener en cuenta en el diseño e implementación de un inversor trifásico tolerante a fallas.

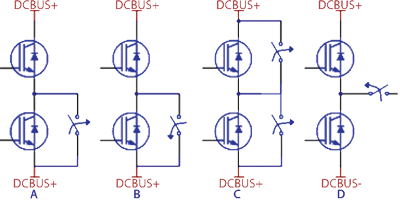

Particularmente, consideramos tres tipos de fallas de entre las tratadas en la bibliografía, para más detalles se puede recurrir a Welchko et al. (2003) para una completa descripción de los métodos de detección y diagnóstico de fallas para inversores trifásicos de tensión.  Figura 2. A) IGBT en cortocircuito; B) IGBT circuito abierto; C) ambos IGBT en cortocircuito; D) fase de motor abierta Figura 2. A) IGBT en cortocircuito; B) IGBT circuito abierto; C) ambos IGBT en cortocircuito; D) fase de motor abierta

Fallas detectables

En la figura 1, se muestra un esquema circuital de un inversor trifásico alimentado con fuente de tensión. En condiciones de funcionamiento normal, entrega a su salida una señal PWM que tiene como componente fundamental el conjunto de tensiones trifásicas senoidales de amplitud y frecuencia deseadas. En la literatura mencionada se tratan cuatro tipos de fallas, que se muestran en la figura 2. Estas fallas son: cortocircuito en una de las llaves de una de las ramas, circuito abierto en una de las llaves de una de las ramas, cortocircuito de las dos llaves de una de las ramas del inversor y la apertura o falta de corriente en una de las tres fases. Esta última falla, que no es del inversor propiamente dicho, es por ejemplo la pérdida de corriente por una de las fases de la carga. En estas condiciones este operaría en dos fases, situación que, además de afectar el rendimiento del motor, afecta su integridad.

En este trabajo se pueden detectar las fallas de apertura de una de las fases y cortocircuito de una de las llaves y cortocircuito en una de las ramas (las dos llaves) del inversor. Particularmente, este convertidor cuenta con una rama extra que puede incorporarse cuando alguna de las ramas del inversor sano entra en falla. El proceso de reconfiguración se realiza mediante un circuito anexado que se encarga de la desvinculación de la rama fallada y la vinculación de la rama de respaldo y un algoritmo de detección y reconfiguración que se implementa en un procesador de señal digital y comanda los operadores de compuerta (o drivers) de los dispositivos de potencia (o llaves de potencia). El algoritmo implementado se basa en una modulación vectorial, la cual se utiliza para el encendido y apagado de las llaves de potencia.

Para detectar la falla de fase abierta se debe sensar constantemente la corriente por las tres fases del motor, ya que la apertura de fase puede darse en cualquiera de las tres fases. Para ello se debe contar con un dispositivo capaz de medir esta corriente en todo instante.

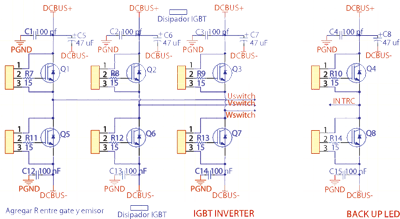

Las segunda y tercera fallas detectables por el equipo propuesto corresponden al cortocircuito de uno o de los dos dispositivos de potencia (llaves) de una de las ramas. Dicha condición puede producirse cuando se disipa más potencia de la permitida en una de las llaves (o ambas de una misma rama) provocando su destrucción. En esta situación, la llave debe estar conduciendo y en lugar de tener tensión drain-source (DS MOSFET) o colector-emisor (CE, IGBT) igual a la tensión típica en saturación, se tendrá una tensión considerablemente mayor. En condiciones de operación normales, cuando la llave está conduciendo se tiene tensión de compuerta alta y tensión DS o CE igual a la de saturación que corresponde a cada dispositivo. Si uno de los semiconductores presentase una falla del tipo de desaturación, lo que implica que ante una tensión de encendido del semiconductor este no tenga a la tensión de saturación en los terminales DS o CE, entonces este dispositivo comenzará a disipar mas potencia y por ende se tendrá como futuro inmediato su rotura, poniéndolo en cortocircuito y así generando la falla de cortocircuito. Para poder detectar este tipo de falla, se requiere de un dispositivo que reconozca las situaciones de operación mencionada. Como se ve, las fallas de cortocircuito de una o de las dos llaves de una rama pueden ser detectadas pero no pueden diferenciarse por lo tanto el diagnóstico es el mismo en los dos casos.  Figura 3. Ramas principales de inversión mas rama de respaldo Figura 3. Ramas principales de inversión mas rama de respaldo

Circuito de potencia

La figura 3 muestra el esquema circuital del inversor propuesto. Este convertidor posee una cuarta rama de inversión. Esta es la encargada de entrar en funcionamiento cuando cualquiera de las otras tres se encuentre en fallas.

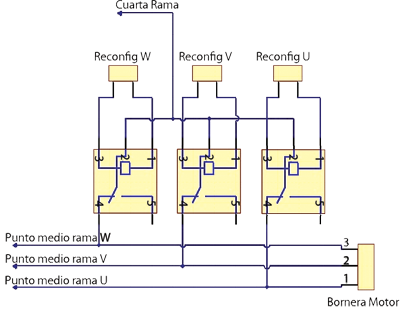

Circuito de reconfiguración

La vinculación galvánica entre el inversor, la rama de respaldo y la carga se realiza mediante un conjunto de relés tal como se observa en la figura 4, que estarán activos o no dependiendo de si existe o no una falla en el sistema. En la parte inferior de la figura se observan las salidas del inversor, notadas como punto medio rama W,V,U que se conectan a la bornera de conexión de la carga. También se observan tres relés, cada uno conecta una salida del inversor con la rama de respaldo.

Durante el funcionamiento normal, los relés presentes en la figura 4 se encuentran en su estado NA (normal-abierto), es decir la rama de respaldo se encuentra desvinculada de la carga. Cuando alguno de los sensores utilizados para detectar las fallas encuentra la presencia de alguna, estos se lo informan al DSP mediante un circuito lógico y de adaptación de niveles de corriente y tensión para que el DSP tome las acciones preestablecidas para lograr la reconfiguración. En primer lugar deja de enviar disparos de encendido a los IGBT de la rama fallada (lo que equivale a abrir ambos semiconduntores) y luego habilita el relé correspondiente a dicha fase, es decir pasar este relé a su estado NC (normal-cerrado) vinculando así la cuarta rama para que esta sea ahora la encargada de reemplazar la rama en falla.

Control tolerante a fallas

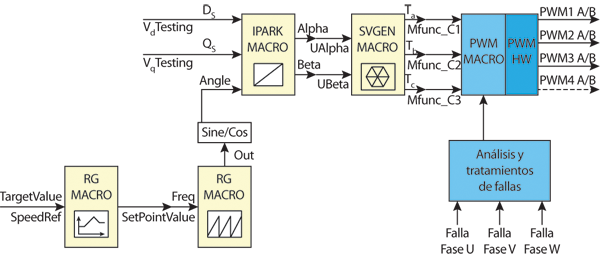

El sistema completo opera a lazo abierto, es decir que no hay ningún tipo de control para el motor, sino que solo se alimenta por las tensiones de salida del inversor y por lo tanto no son necesarias mediciones como la velocidad del eje del motor.

En presencia de fallas, los sensores de corriente y tensión, entregan señales lógicas al DSP, que activará el relé correspondiente a la rama en falla y conectará la de respaldo y enviará las tensiones de excitación de los IGBT a esta última.

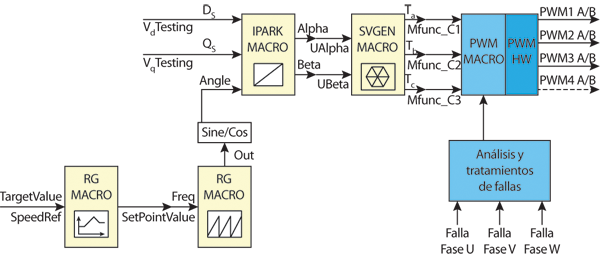

Figura 4. Esquema de reconfiguración El conjunto DSP más el circuito de detección de fallas propuesto sensa el estado de todas las posibles fallas que puede presentar el inversor y actúa de acuerdo a lo expresado en el párrafo anterior. En la figura 5 puede verse el esquema modular de las macros utilizadas en el código implementado en el DSP. En dicho diagrama se pueden ver los bloques asociados a la modulación vectorial y los bloques asociados a la detección y diagnóstico de fallas, las salidas de estos bloques convergen a la unidad de recofiguración que tiene como salidas las señales que comandan las llaves del inversor y que están notadas como PWM1, PWM2, PWM3 y PWM4. Figura 4. Esquema de reconfiguración El conjunto DSP más el circuito de detección de fallas propuesto sensa el estado de todas las posibles fallas que puede presentar el inversor y actúa de acuerdo a lo expresado en el párrafo anterior. En la figura 5 puede verse el esquema modular de las macros utilizadas en el código implementado en el DSP. En dicho diagrama se pueden ver los bloques asociados a la modulación vectorial y los bloques asociados a la detección y diagnóstico de fallas, las salidas de estos bloques convergen a la unidad de recofiguración que tiene como salidas las señales que comandan las llaves del inversor y que están notadas como PWM1, PWM2, PWM3 y PWM4.

Si el inversor opera en condiciones de funcionamiento normal, el DSP tendrá como salidas activas las señales PWM1, PWM2, PWM3 que corresponden las ramas U,V,W del inversor. En caso de una falla, por ejemplo en la rama U, lo que realiza el código en primer lugar poner en estado bajo los gate de los IGBT de la rama U, luego se activa el relé que conecta la rama de respaldo sacando de servicio la rama que presenta la falla y conecta la rama de respaldo. Por último, activa el PWM4 que, ení́a los mismos pulsos que el 1 pero en este caso se los entrega a los IGBT de la cuarta rama.

Detección de fallas

Para la detección de las fallas propuestas se necesita medir las corrientes de fase y las tensiones colector-emisor de los IGBT. Para ello, se requieren dos tipos de sensores. A continuación, se explica qué elemento se utiliza y qué variable se mide para poder detectar cada una de las fallas.  Figura 5. Esquema de reconfiguración Figura 5. Esquema de reconfiguración

Falla fase abierta

Para la detección de este tipo de falla se utilizan bobinas arrolladas en núcleos toroidales especiales para poder sensar en todo momento la corriente por cada una de las tres fases. El esquema básico de este sensor se muestra en la figura 6. Estos sensores están constituidos por un toroide propiamente dicho y por un circuito interno que se encarga de rectificar la tensión que se induce en la bobina de este sensor, ya que el conductor de una de las fases del motor pasa por dentro del sensor toroidal, esta tensión rectificada es integrada y comparada con un valor de referencia (que se elige dependiendo de la tensión inducida). Si el valor medido resulta mayor que dicho umbral se disparará un transistor NPN (integrado en el sensor) y si el valor medido se mantiene por debajo de este umbral dicho transistor se mantendrá abierto.

El funcionamiento normal corresponde al transistor NPN saturado, es decir que hay corriente circulando por la rama del inversor y por lo tanto se induce corriente en la bobina toroidal. Este estado de saturación le indica al circuito de reconfiguración que el estado de las ramas U, V y W es correcto. Si por alguna razón se interrumpe la corriente por la rama del inversor, no se induce corriente y en consecuencia el transistor saldrá de su estado de saturación, este cambio en la salida indica la presencia de una falla.

Este tipo de sensor es pasivo y es fácilmente accesible en el mercado, lo que lo hace apropiado para esta aplicación.

Por último, se busco que todos los sensores, drivers y circuitos fueran lo más rápidos posibles en comparación con la frecuencia de conmutación del convertidor, dado que una aplicación de este tipo requiere que cada elemento que lo componga actúe velozmente ante cualquiera de falla y así evitar daños irreversibles en el convertidos y en la carga.

Figura 6. Esquema circuital del toroide para el sensado de corriente

Falla por cortocircuito

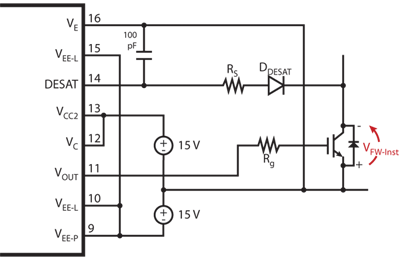

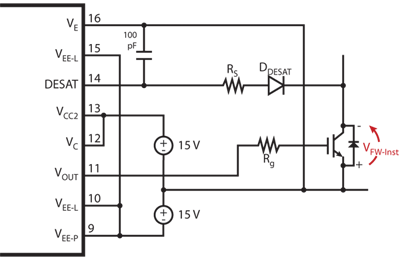

Para la detección de la falla por cortocircuito se eligió un tipo operador de compuerta para los IGBT que tiene una característica que lo hace apropiado para el diseño propuesto. Tal característica es el sensado de tensión CE del IGBT o también llamado sensado de desaturación. Este se lleva a cabo mediante el arreglo de una resistencia, un capacitor y diodos en serie como puede verse en la figura 7. El sensado se basa en que los IGBT al momento de encenderse pasan de la región de corte a la región de saturación, es decir, su tensión CE debe ser de apenas 1,9 volts, en el caso que este valor estuviese por encima del valor típico de saturación del IGBT, se activará la señal de falla (que es enviada al DSP). Además, el mismo driver es capaz de anular internamente la señal que enciende a los IGBT. Por lo que este sensor desvincula automáticamente a este IGBT y luego el DSP confirma esta acción anulando la señal PWM correspondiente. Los pines 14 y 16 del driver conjuntamente con la resistencia, capacitor y diodos mencionados se utilizan para el sensado, tal como puede verse en la figura 7.

Figura 7. Esquema de sensado de desaturación Figura 7. Esquema de sensado de desaturación

Dimensionamiento general

El inversor propuesto tiene principalmente fines académicos y de investigación por lo tanto fue diseñado para trabajar con cargas de poca potencia. En particular, para esta aplicación se conectó a un motor de inducción trifásico de 1/3 HP de potencia. Con esta carga se dimensiona el bus de tensión continua:

VBUS = 220 Vrms • √2 ≈ 311 V [1]

Adoptando como criterio de diseño que en general los motores poseen un rendimiento de aproximadamente η motor igual a 0,75 y, además, considerando un rendimiento del inversor de η inversor igual a 0,95, se tiene que:

Pmotor eléc. = Pmotor mec. /ηmotor ≈ 331 W [2]

Pin inversor = Pinversor/ηinversor ≈ 350 W [3]

Con los resultados de las ecuaciones 2 y 3 sabemos que para hacer funcionar al motor en condiciones nominales será necesario que el bus de tensión continua (compuesto por un puente rectificador y un banco de capacitores) entregue una tensión de VBUS igual a 220 Vrms y una corriente de:

Iinversor = Pin inversor/VBUS ≈ 1,12 Arms [4]  Figura 8. Señales PWM de ramas de inversión Figura 8. Señales PWM de ramas de inversión

Selección de semiconductores

Existen varios factores claves que definen qué semiconductores utilizar, entre estos factores pueden mencionarse la frecuencia a la que trabajará el inversor y su potencia, que es equivalente a decir los valores de tensión y corriente que deberá manipular. Al conocer las características de la carga con sus valores de tensión y corriente y también la frecuencia de trabajo, ya se sabe que los valores de tensión y corriente que deberá manejar el inversor no son tan críticos en la elección del semiconductor, sin embargo la frecuencia de conmutación juega un rol fundamental, es por esto que se optó por seleccionar IGBT. Según los criterios aquí expresados, se seleccionaron los dispositivos teniendo en cuenta las siguientes características:

-

Elevada conducción de corriente, igual a sesenta amperes

-

Pequeña tensión de saturación, igual a 1,9 volts

-

Elevada impedancia de entrada, diez megahoms aproximadamente

-

Frecuencia conmutación alta, 100 Hz ≤ fs ≤ 500 KHz

Figura 9. Señales PWM con reconfiguración activa Figura 9. Señales PWM con reconfiguración activa

Resultados experimentales

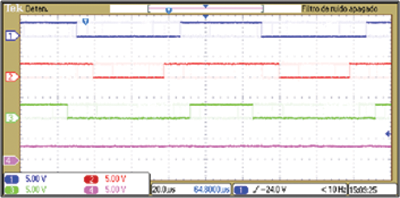

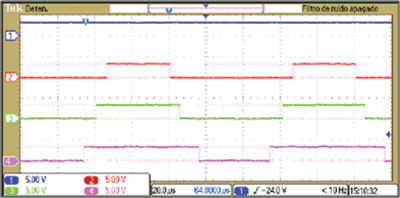

Los primeros ensayos fueron solo con el DSP, que permitieron verificar el buen funcionamiento del algoritmo de implementación de la estrategia de reconfiguración del inversor. Luego se ensayaron los circuitos de detección y reconfiguración y por último todo el conjunto inversor-motor de inducción. La frecuencia de conmutación del PWM es de diez kilohertz.

En la figura 8 se presentan las salidas de un osciloscopio de cuatro canales. Los canales 1, 2, 3 muestran las señales PWM de salida del DSP cuyos valores oscilan entre cero y 3, 3 volts. Estas señales ingresan a un circuito de adaptación de niveles que activan los gate-driver de los IGBT de las ramas del inversor base, anotadas como U, V y W, respectivamente. Puede verse cada una de ellas con sus desfasajes correspondientes de forma tal de evitar cortocircuitos en el bus de tensión continua.

La cuarta salida del osciloscopio corresponde a la rama de respaldo del inversor y que, dado que el inversor funciona en forma normal, se encuentra inactiva en estado alto. Para poder verificar el funcionamiento de esta parte del equipo se simuló una falla en la fase U para así poder ver el traspaso del control de la rama U a la rama de respaldo, es decir, los disparos que antes se observaban en el la rama U pasan a la cuarta rama y consecuentemente dejan de pasar a la rama U donde se presentó la falla, como puede apreciarse en la imagen de la figura 9.

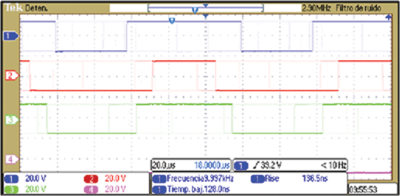

Luego de verificar el funcionamiento correcto del DSP, se verificó el funcionamiento de los circuitos adaptadores de señal que adaptan la salida del DSP de cero a 3,3 volts y la eleva a un rango de cero a cinco para ingresar en los drivers u operadores de compuerta de los IGBT. Estos drivers se encargan de sumar o restar quince volts, aproximadamente, entre el gate y el emisor de todos los IGBT, ya sea para encenderlo o para asegurar el apagado. En la figura 10, pueden verse las señales de excitación de los drivers.

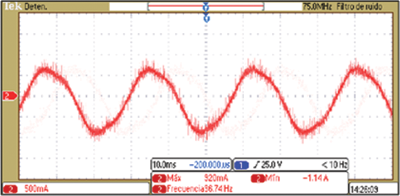

Figura 10. Señales a la salida de los gate-drivers en funcionamiento normal Para el ensayo está completo, el inversor y el motor trifásico mencionado trabajan en vacío. Se verificó el correcto funcionamiento del conjunto en condiciones sanas. En la figura 11 se muestra la tensión de fase V del motor. Dado que el motor está conectado en triángulo, la tensión observada por el osciloscopio es el valor real. La figura 12 muestra la corriente de fase del motor que es baja debido a que el motor está trabajando en vacío. Figura 10. Señales a la salida de los gate-drivers en funcionamiento normal Para el ensayo está completo, el inversor y el motor trifásico mencionado trabajan en vacío. Se verificó el correcto funcionamiento del conjunto en condiciones sanas. En la figura 11 se muestra la tensión de fase V del motor. Dado que el motor está conectado en triángulo, la tensión observada por el osciloscopio es el valor real. La figura 12 muestra la corriente de fase del motor que es baja debido a que el motor está trabajando en vacío.

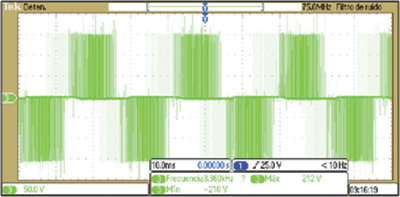

Por último se realizó un ensayo del conjunto inversor-motor en presencia de fallas. Se procedió a abrir la fase U del motor mediante un relé. Aquí se verificó que el mecanismo de detección de falla funcionara correctamente. En la figura 13 puede verse la corriente por la fase mencionada antes de realizar la apertura de la rama (parte superior), el instante justo en el que se queda sin corriente (parte intermedia) y por último cuando vuelve a tener corriente luego de la reconfiguración (parte inferior). Finalmente en la figura 14 muestra la implementación final del convertidor.  Figura 11. Tensión en el bobinado de fase V Figura 11. Tensión en el bobinado de fase V

Conclusiones y trabajos futuros

En este trabajo se presentó el diseño y la implementación de un inversor tolerante a fallas. Dicho convertidor posee una cuarta rama que entra en funcionamiento cuando se presentan fallas de apertura de una de las fases de la carga, cortocircuito de una o de las dos llaves de una de las ramas del inversor. Se realizaron ensayos que verificaron el buen funcionamiento del equipo en condiciones normales y bajo falla utilizando un motor de inducción como carga. Como trabajo futuro, se plantea implementar un mecanismo de reconfiguración que no involucre una cuarta rama, de ese modo el sistema no necesitaría redundancia pero perdería desempeño.

Referencias

Figura 12. Corriente senoidal por la fase V del motor Fu, J y T Lipo (1993). “A strategy to isolate the switching device fault of a current regulated motor drive” en Conference Record de 1993 IEEE Industry Applications Society Annual Meeting, 1993. Toronto, pp. 1015-1020 vol.2

Liu, Tian-Hua, Jen-Ren Fu y T.A. Lipo (1993). “A strategy for improving reliability of field-oriented controlled induction motor drives” en IEEE Transactions on Industry Applications 29(5), 910-918

Nacusse, M., M. Romero, H. Haimovich, M. Seron y S. Junco (2012). “Model predictive control for induction motor control reconfiguration after inverter faults” en Journal Europén des Systémes Automatisés 2, 1015-1020

Welchko, B.A., T.A. Lipo, T.M. Jahns y S.E. Schulz (2003). “Fault tolerant three-phase AC motor drive topologies: A comparison of features, cost and limitations” en IEEE Transactions on Power Electronics 1, 539-546

Yznaga Blanco, I, S Dan y H Yi-kang (2008). “Study on inverter fault-tolerant operation of PMSM DTC” en Journal of Zhejiang University Science A 9(2), 156-164

Nota del editor. La nota aquí publicada fue originalmente presentada por los autores como artículo técnico del área estudiantil en AADECA 2016, Semana del Control Automático - 25 o Congreso Argentino de Control Automático, celebrado en la ciudad de Buenos Aires entre el 1 y el 3 de noviembre de 2016

|